자일링스가 한 달 사이에 두 개의 기술을 발표했다. 발표한 기술은 새로운 RFSoC 디바이스와 머신 러닝 애플리케이션 확대를 위한 reVISION 스택이다. 이 두 가지 기술 발표를 통해 자일링스는 5G와 머신 러닝을 겨냥하며 두 기술이 업계에서 갖는 존재감을 다시 한 번 상기했다.

우선 RFSoC 디바이스에 관한 발표를 살펴보고자 한다. 지난 2월 15일 여의도에 위치한 자일링스 한국지사 사무실에서 기술 발표가 이루어졌다. 자일링스의 FPGA 플랫폼 마케팅 부사장인 팀 엘야백(Tim Erjavec)과 통신 사업 부분 이사인 하핀더 마따루(Harpinder S Matharu)가 한국을 방문하여 이 날 발표에 참여했다.

▲ 자일링스 FPGA 플랫폼 마케팅 부사장 팀 엘야백

올프로그래머블 디바이스 RFSoC 출시

자일링스는 기술 발표에 앞서 업계가 5G에 진출하는 데 어떤 어려움이 있는지 진단했다. 우선 모바일 장비 제조업체가 기술 시험 및 개념 입증 테스트에 상당한 관심을 보이고 있어서 이러한 구현이 상용화될 가능성에 대해 평가하고 있지만, 프로토타입핑(prototyping)에 사용되는 기술의 상당 부분이 상용화 단계로 옮겨가지는 못할 것이라는 우려를 표했다. 또한 자일링스는 스펙트럼 효율성 문제와 고밀도 배치 문제, 에너지 효율 문제도 업계의 과제라고 말했다.

이를 해결하기 위한 솔루션으로 자일링스는 RFSoC 디바이스(그림1)를 출시하며 16나노 올 프로그래머블 MPSoC에 RF급 아날로그 기술을 융합하고 5G 무선통신에서 획기적인 통합 및 아키텍처 혁신을 제공할 것이라고 발표했다. RFSoC 디바이스를 통해 디스크리트 데이터 컨버터를 제공하고, 이로 인해 5G 매시브 MIMO 및 밀리미터파 무선 백홀 애플리케이션에서 50-75%의 전력 및 풋프린트(footprint) 감소가 가능해진다는 것이다.

▲ 그림 1. 자일링스의 올프로그래머블 디바이스 RFSoC

RFSoC는 디지털 처리 서브시스템, 강력한 RAM 급 처리 시스템, FPGA 패브릭과 같은 통신 등급 RF 샘플링 데이터 컨버터를 모두 모아 놓은 모놀리식 디바이스다. 아날로그 디지털 신호 체인은 아날로그 설계자가 유연하게 구성할 수 있도록 강화된 DSP 서브시스템에 의해 지원될 수 있어서 전력 및 풋프린트 감소와 진화하는 네트워크 토폴로지에 맞추는 데 유연함을 갖췄다.

전력 및 폼팩터 감소가 기술 포인트

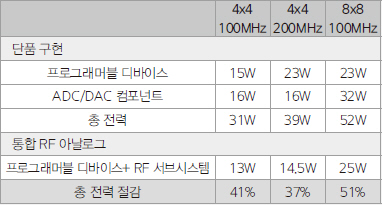

자일링스가 발표 내내 거듭 강조했던 전력 및 폼팩터 크기 감소에 대해 자세히 살펴보자. 표 1을 보면 전형적인 안테나 구성은 단품 ADC와 DAC가 소비하는 전력이 매우 크다. 반면 ADC와 DAC를 통합한 RFSoC는 기본 구성에 비해 40%나 전력 감소가 가능하다.

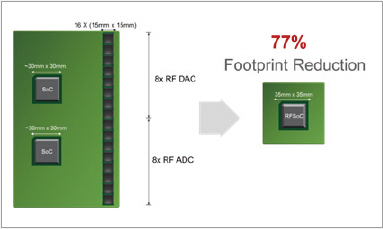

그림 2에서는 폼팩터 크기 감소에 대해 살펴보 수 있다. 전력 소비와 마찬가지로 전형적인 구성에서는 RF ADC나 DAC가 채널 당 보드에서 최대 15x15mm를 차지할 수 있는데 그림 2를 보면 더 큰 라디오 구조의 경우, 급격히 폼팩터를 줄일수 있어 완전히 배치 가능한 멀티 채널 시스템을 75% 이상 감소 가능하다.

▲ 그림 2. 8Tx8Rx 전파의 폼팩터 감소

직접적인 RF 샘플링의 가치

전력과 폼팩터 문제 외에 RF 샘플링 기술 기반의 컨버터 서브시스템도 RFSoC의 장점으로 들 수 있다. 지금까지 대부분의 시스템은 중간 주파수 샘플링이라는 아날로그 기반 전략을 구현했다. 여기서 원래의 신호가 ADC 샘플 속도에 의해 지원되는 주파수로 다운 변환된다. 다운 변화 회로는 믹서, 고품질 오실레이터, 기타 아날로그 부품으로 이루어져 있다. 이 아날로그 회로는 비교적 유연성이 떨어져 특화된 설계와 복잡한 부품 선정을 필요로 한다.

자일링스는 자사의 RF 샘플링 방식이 입력되는 RF 신호는 초기의 다운 변화 없이 직접 샘플링 된다. 이 신호가 디지털화되면 보다 유연한 다운 변환과 신호 처리가 보다 디지털 도메인상에서 이루어질 것이라고 한다. 이 샘플 속도가 높을수록 디지털 도메인에서의 다이내믹 레인지, 신호 품질(SNR), 신호 대역폭 간의 균형이 개선된다는 것이다.

디지털 도메인에서의 완벽한 유연성과 더불어 라이도 프로세싱을 안테나에 더 가까이 이동시키기 위해 자일링스는 SoC를 통합함으로써 이 방식을 한 단계 더 발전시켰다. 이로 인해 모바일 장비 공급업체는 동일한 디바이스를 이용해 다양한 Tx/Rx 안테나 구성 및 진화된 표준을 처리할 수 있어서 시장 역학 및 기회기 신속하게 대응할 수 있을 것으로 기대된다.

5G 시장을 위해 꼭 필요한 기술

자일링스는 이 날 발표한 기술을 무려 10년 전부터 계획해왔다고 한다. 2012년에 처음 기술 테스트가 시작되었고 이렇게 발표될 때까지 계속해서 개발하고 연구하였기 때문에 이번에 발표한 RFSoC 기술이 안정적으로 구현될 수 있다고 확신했다.

현재 업계에서는 5G가 안정적으로 전개될 수 있는 시기를 2020년쯤으로 예상하고 있어서 지금은 ‘Pre-5G’ 시대라고 볼 수 있겠다. 5G 기술을 원하는 무선통신 고객사들은 기술을 전개하기 위해 지속적으로 자일링스에게 기술 관련 연락과 요구를 해왔다고 한다. 자일링스의 FPGA 플랫폼 마케팅 부사장 팀 엘야백은 “고객사들의 요구 때문에 RFSoC 기술이 만들어졌고 우리와 같은 기술을 도입하지 않으면 5G를 구현하는 데 매우 어려울 것이다”라며 자사 기술에 대한 자신감을 나타냈다.

reVISION 기술 통해 비전 기반 머신 러닝 애플리케이션 범위 확장

2월 22일에는 자일링스의 reVISION 기술 발표가 이루어졌다. 이날도 RFSoC 발표와 마찬가지로 미국 본사에서 담당자들이 직접 한국을 찾았다. 발표에 참여한 담당자는 기업전략마케팅 그룹의 수석부사장 스티브 글레이저(Steve Glaser)와 임베디드 비전 및 SDSoC 부문 수석 제품 매니저 닉 니(Nick Ni)이다.

▲ reVISION에 대해 설명하고 있는 자일링스 기업전략마케팅 그룹의

수석부사장 스티브 글레이저

reVISION은 플랫폼, 알고리즘, 애플리케이션 개발을 위한 다양한 개발 리소스를 포함하는 스택이다. 여기에는 AlexNet, GoogLeNet, SqueezeNet, SSD 및 FCN과 같은 많이 사용되는 신경망에 대한 지원이 포함되어 있다. 또한 자일링스는 사용자 정의 신경망(DNN/CNN)을 구축하는 데 필요한 CNN 네트워크 레이어를 위해 미리 정의되고 최적화된 구현을 비롯한 라이브러리 요소를 제공한다. 하드웨어에 대한 전문 지식이 없어도 광범위한 설계팀이 소프트웨어 정의 개발 흐름을 이용할 수 있다는 점도 주목할만한 부분이다. 설계팀은 이 스택을 이용하여 머신 러닝 및 컴퓨터 비전 알고리즘의 구현을 시스템에 결합할 수 있다.

보다 쉬운 머신 러닝 애플리케이션 개발 도모

머신 러닝 관련 시장에서는 차별화가 매우 중요함은 물론이고 시스템의 반응 속도가 즉각적이어야 하며, 최신 알고리즘 및 센서를 신속하게 배치해야 한다. 자일링스의 reVISION은 이 점을 커버할 수 있는 기술로써 차세대 애플리케이션인 협업로봇 ‘코봇(Cobots)’과 ‘감지 후 회피(sense and avoid)’하는 드론, 증강 현실, 자율주행차, 자동화 감시, 의료 진단 등을 지원할 수 있다.

앞서 말한 애플리케이션에는 일반적으로 3가지 명령이 필요하다. 우선 시스템은 생각할뿐만 아니라 상황에 대해 즉각적으로 ‘반응’해야 하며, 신경망과 관련 알고리즘, 센서가 신속하게 변화하기 위해 시스템을 유연하게 업그레이드해야 한다. 또한 이러한 시스템 대부분이 기존 머신은 물론 미래에 등장할 새로운 머신 및 클라우드와도 대화할 수 있어야 한다.

자일링스의 디바이스는 위 세 가지 명령을 수행할 수 있다. 효율적인 추론 및 제어를 통해 빠른 반응 시간을 가능하게 하며, 재구성 가능한 능력으로 신경망, 알고리즘, 센서를 지원하고 any-to-any 커넥티비티로 기존의 머신뿐만 아니라 새로운 머신과 클라우드에 대한 접속을 지원한다.

▲ 표 1. 통합 서브시스템을 이용한 디지털 라디오(DPD 이용)에서의 전력 감소

센서에서 추론제어까지 확 낮춘 레이턴시

앞서 말한바와 같이 애플리케이션 명령에서는 즉각적 반응이 매우 중요하다. reVISION 플로우는 반응성이 신속하여 시스템 개발을 가능하게 하는데, 자일링스 측의 발표에 따르면 임베디드 GPU와 일반 SoC의 성능을 비교했을 때 자일링스가 이 분야 최고인 엔비디아(Nvidia)를 넘어서고 있다고 한다.

reVISION 플로우를 엔비디아 Tegra X1과 비교해보았다. reVISION 플로우는 머신 러닝에서 6배 뛰어난 이미지/초/와트를, 컴퓨터 비전 처리에는 초당 42배 더 높은 프레임을, 실시간 애플리케이션에서 무엇보다 중요한 레이턴시는 1/5 수준이다.

자일링스의 reVISION은 징크 기반 플랫폼의 고유한 강점과 업계 표준 라이브러리 지원을 탑재한 소프트웨어 정의 개발 환경이 결합되어 비전 기반 시스템 개발에서 좋은 대안이 될 것으로 기대된다.

발표를 진행했던 자일링스 기업 전략 그룹 수석 부사장 스티브 글레이저는 “자일링스는 에지에서 클라우드까지 머신 러닝에 엄청난 관심을 지켜보고 있는 중이며, 개발 스택에 대한 지속적인 투자는 이 채택의 흐름을 가속시킬 것이다”라고 밝혔다. 업계에서 머신 러닝이 갖는 존재감에 대해 다시 한 번 확인할 수 있는 말이 아닐까 싶다.

자일링스의 발표는 향후 업계가 어떤 부분에 집중해야하는지 알려주고 있다. 5G, 그리고 머신 러닝이 자일링스를 비롯해 관련 기업들에 의해 어떻게 발전될지 기대가 된다.

정가현 기자(eled@hellot.net)